Asynchronous reset versus synchronous reset:

One of the main drawbacks of asynchronous reset is that it can turn a digital design into an asynchronous sequential circuit, which is more complex and harder to predict. This can lead to timing issues, especially if the reset signal is not properly synchronized with the clock. For example, if the reset signal has glitches or transitions at the same time as the clock edge, it may cause the flip-flop to enter an unstable state, potentially leading to incorrect outputs and reduced system reliability.

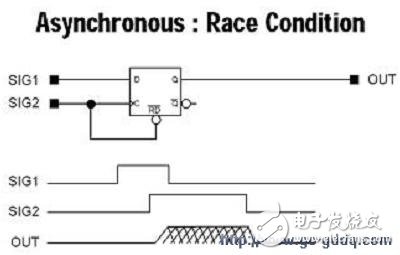

Additionally, when the relationship between the reset signal and the clock is uncertain, metastability can occur. Metastability is a condition where a flip-flop fails to settle to a stable logic level within the required time, resulting in unpredictable behavior. Below is an example that illustrates how this can happen.

In Figure 1, we see an asynchronous race condition involving a clock signal used to reset a flip-flop. When SIG2 is low, the flip-flop is reset to a low state. On the rising edge of SIG2, the designer expects the output to transition to the high state of SIG1. However, due to unknown internal timing and routing delays, it's unclear whether the clock edge or the reset signal will arrive first. If the clock edge arrives first, the output might go low. If the reset signal arrives first, the output might go high. Small variations in temperature, voltage, or manufacturing process can cause unexpected failures in otherwise working designs.

So what exactly is a metastable state? According to Howard Johnson’s book "High-Speed Digital Design: A Handbook of Black Magic," metastability occurs when the input to a logic circuit doesn’t have enough time to reach a stable logic level before the circuit samples it. This can result in the circuit taking longer than expected to settle into a valid output state. This extra time is referred to as the resolution time.

In one of his examples (page 123, section 3.11.2), Johnson uses a flip-flop to demonstrate metastable behavior. He simulates the flip-flop using an amplifier, two switches, and a capacitor. The capacitor holds the logic level, while the switches simulate data input and clock transitions. Before the flip-flop triggers, the input data is stored in the capacitor. Then, switch S1 disconnects the input, and the amplifier begins the internal flipping process through a positive feedback loop.

Once switch S1 is disconnected and switch S2 (on the feedback loop) is closed, the amplifier enters an intermediate, unstable state. This can be modeled as:

V(out) = V(in) × exp(kt).

Here, V(in) represents the input voltage level, V(out) is the output, and k is a constant related to the amplifier's bandwidth and the feedback loop. If the sampling time is too short, the capacitor doesn’t fully charge, and the output remains in an unstable, intermediate state for a longer period. This delay is what we call metastability.

From Johnson’s experiments, it becomes clear that as the timing margin decreases, the circuit's response slows down. Eventually, when the margin is too small, the circuit may fail to produce a valid output altogether.

Therefore, metastability is a serious issue in high-speed digital design. It can cause unpredictable behavior, reduce system reliability, and make timing analysis significantly more challenging. To mitigate this, designers must ensure sufficient timing margins and carefully manage reset and clock signals to avoid metastable conditions.

Original Bang Vape 8000,Original Bang 8000 Puffs,Bang King 8000 Puffs Vape

Longhua Manxueling Trading Company , https://www.mxlvape.com