Asynchronous reset has several differences compared to synchronous reset. Under normal conditions, when the relationship between the reset signal and the clock is well understood, the main drawback of asynchronous reset is that it turns the design into an asynchronous sequential circuit. If the reset signal has glitches, it can cause the flip-flop to malfunction, leading to instability in the overall system.

Moreover, if the timing relationship between the reset and the clock is uncertain, it can lead to metastability issues. Let’s look at an example below to better understand this phenomenon.

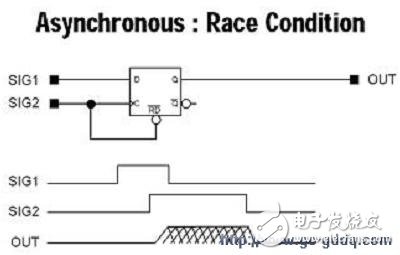

Figure 1 shows an asynchronous race condition where a clock signal is used to reset a flip-flop. When SIG2 is low, the flip-flop is reset to a low state. On the rising edge of SIG2, the designer expects the output to transition to the high level of SIG1. However, due to unknown internal timing of the flip-flop or routing delays between the clock and reset signals, we cannot determine which signal arrives first. If the clock edge arrives first, the output may go low. If the reset signal arrives first, the output may go high. Even small variations in temperature, voltage, or manufacturing process can cause unexpected behavior in an ASIC that was designed to work correctly.

Metastability is a critical issue in digital design. According to Howard Johnson’s book "High-Speed Digital Design: A Handbook of Black Magic," metastability occurs when the input to a logic circuit doesn't have enough time to settle at the required logic level. This results in the circuit needing extra time to stabilize its output, known as the resolution time. In Johnson's example, a capacitor is used to maintain the logic level of a device. If the timing is insufficient, it's like charging a capacitor—there's a delay before the output reaches a stable state.

In the book, Johnson uses a flip-flop example (page 123, section 3.11.2) to illustrate metastable behavior. He simulates the flip-flop using an amplifier, two switches, and a capacitor. The capacitor holds the logic level, and the switches simulate the data input and the flip-flop's operation. Before the flip-flop changes state, the input data is stored in the capacitor. Then, switch S1 disconnects the input, and the flip-flop begins its internal transition through the amplifier with a positive feedback loop.

Once switch S1 is disconnected and switch S2 on the feedback loop is closed, the amplifier enters an intermediate, unstable state. This can be modeled as:

V(out) = V(in) * exp(kt)

Where V(in) is the input voltage level, V(out) is the output voltage, and k is a time constant related to the amplifier’s bandwidth and the feedback loop.

If the flip-flop samples the input for too short a period, the timing margin is insufficient, causing V(in) to be small. This means the output takes longer to reach a stable level, resulting in a prolonged metastable state. The circuit becomes slower to respond, which is what we refer to as metastability.

From Johnson’s experiments, we see that as the timing margin decreases, the circuit’s response slows down. When the margin is reduced beyond a certain point, the circuit may fail to produce any valid output at all.

The presence of metastability can cause serious issues in digital systems, especially in high-speed designs. Therefore, ensuring sufficient timing margins is crucial to prevent unpredictable behavior and maintain the reliability of the circuit.

Longhua Manxueling Trading Company , https://www.mxlvape.com