As a new generation of video codec technology, H.264 has superior compression performance compared with traditional MPEG-2, enabling it to achieve higher quality video transmission in a smaller bandwidth, occupying video data storage. Fewer storage space.

This article refers to the address: http://

In the traditional DVB-T market, MPEG-2 is the mainstream video codec format. In recent years, as bandwidth and frequency resources become more and more precious, operators in emerging regions of Europe, Russia, and Turkey have chosen H.264 as a video codec format, forming a market of a certain scale, which has attracted the attention of set-top box manufacturers.

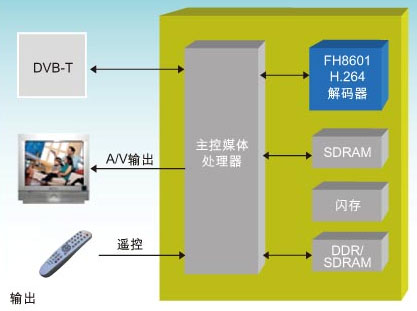

Shanghai Fushun Microelectronics Co., Ltd. saw this demand a few years ago and launched the H.264 decoder chip FH8601. This ASIC chip is combined with the proven DVB-T set-top box chip into a two-chip solution. As a coprocessor, the FH8601 can receive commands from the main chip (such as LSI9700, NEC61123) and H.264 code stream data. After decoding, the image is sent back to the main chip through the 601/656 display interface, and the main chip performs display processing. This program has been selected for mass production by Russian DVB-T operators.

How to implement a new generation of H.264 video decoding capability based on the traditional DVB-T set-top box platform? What key technical problems do engineers need to solve when implementing such a two-chip combination solution? This article will focus on H. The 264 decoder chip FH8601 needs to pay attention to the following technical key points in the process of integration with the traditional platform:

1. Control interface and video I/O interface;

2. Realize video and audio (A/V) synchronization;

3. Coping with H.264 code stream compatibility;

4. Host system software.

Control interface and video I/O interface

As shown, in a set-top box terminal, the FH8601 acts as a coprocessor for video decoding. It provides an interface to the main chip for communication and data transfer, the most basic LocalBus interface. As long as the main chip can provide access to the RAM or Nor type flash data address bus, the FH8601 control and video data transfer can be realized. How the main chip obtains the video data decoded by FH8601 is also a problem that system engineers need to consider. The FH8601 provides a standard ITU601/656 video output interface for this purpose.

The host interface LocalBus: FH8601 chip can transfer data to the host through 16-bit or 8-bit data width, 8-bit or 16-bit width configurable. The operation of the host to the FH8601 mainly includes resetting, configuring, downloading firmware, writing stream data, and query status.

Video data output interface: The video data is fully compatible with the ITU 601/656 standard, and the host must be able to provide the corresponding video input interface. The synchronous clock of the video output interface can be selected from 0 degree phase and 180 degree phase.

Audio and video synchronization

Audio and video synchronization is an issue that should be the focus of all audio and video application engineers developing set-top box solutions. Engineers often spend more time on this technology point to get the best audio and video effects. From the actual effect of the implemented scheme based on FH8601, the effect of audio and video synchronization is very good.

1. Guarantee of audio and video synchronization in MPEG specification

The MPEG specification provides the right tool for absolutely guaranteed audio and video (A/V) synchronization. Each audio and video frame has a display time stamp (PTS) that allows the decoder to reconstruct the sound and image simultaneously. These PTS values ​​are assigned by multiplexers in the MPEG encoder. The decoder receives the audio and video data before these PTSs and can then use these values ​​to play the video and audio simultaneously. In the MPEG system, since bit time slots, road slots, and frames in time division multiplexing have a strict time relationship, this is synchronization. In order to resume the program, the ES is first decoded. The reproduction of sound and image signals needs to be displayed synchronously, so that the data streams at both ends of the transmission and reception are required to be synchronized.

2. Synchronization mechanism provided by FH8601

The FH8601 features automatic audio and video synchronization. This feature simplifies the complexity of the system software. Specifically, the main chip needs to turn on the synchronization function in the FH8601. In the decoding process, the main chip needs to write the current PTS of the audio to the FH8601, so that the FH8601 automatically synchronizes the video and audio. The video PTS is written to the FH8601 along with the code stream data.

Code stream compatibility and scalability

Although the H.264 standard was confirmed as early as 2003, it is still in the early stage of application, and the encoder is far less mature than MPEG2. Therefore, the decoder must face the problem that the code stream is not standard and frequently upgraded. The FH8601 considers how to deal with these issues during the definition phase of the chip implementation. Through the firmware, we implement the flexible part of the standard in software. All changes to the firmware do not require the involvement of the solution design engineer, but simply replace the original firmware and download it online.

Code stream compatibility: Currently, the FH8601 is connected to all mainstream encoders in addition to all ITU compatible bitstream tests.

Online firmware update: When you need to upgrade the firmware, you only need to provide a new firmware data file. The user can directly replace the original file and recompile it to complete the upgrade.

System software design

For emerging solutions such as DVB-T/H.264, any engineer who is reluctant to abandon the original software resources and code accumulation will think of software reuse. Obviously, for design companies that already have DVB-T set-top box solutions, the most direct convenience that a two-chip solution brings to system engineers is that all system resources can be placed directly in new projects. In the following, we also need to consider the reuse of the original software resources. In fact, the original software and code will not be wasted if the host has not changed, unless you think they are out of date. We only need a small number of driver porting and interface function call test work according to the newly added H.264 decoding function.

Comparison of different programs

Market risk: From a technical point of view, the two-chip solution consisting of FH8601 and mature DVB-T chips is compared with other single-chip SoC solutions supporting H.264 decoding, in terms of R&D investment, development cycle, and program maturity. The obvious advantages can greatly reduce the risk of products entering the market.

Price advantage: At the same time, from the price point of view, since the original DVB-T chip has been shipped in large quantities, the market price has been very low, plus a low-cost H.264 decoder FH8601, the BOM price of its set-top box terminal Compared with other SoC single-chip-based terminals, the BOM price is 30% to 50% lower.

Development inheritance: For the single-chip SoC solution currently on the market, when designing such a solution, the design company basically gave up the accumulation of the original software resources, adopting a new software architecture and middleware resources, and the software developer needs to restart a new one. The learning of the platform will inevitably lead to an increase in the entire code development cycle and an increase in test tasks. The wait for the market is also a long process.

From the description of the video part in the single-chip SoC solution, we can see that they have a wide range of standards for video support, representing several standard H.264, VC-1, etc. that may appear in the future. At the same time, the functions are diversified and flexible, and the terminal cost increases. The dual-chip solution using the FH8601 is specifically targeted at the H.264 SD decoding market, which meets the needs of the current market.

FGI`s FGSVG series low voltage dynamic reactive power compensation and harmonic devices are mainly composed of control panels, energy storage capacitors, reactors, IGBT, inverters, fuses and other devices. The Low Voltage Static Synchronous Compensator (STATCOM) has functions such as compensating reactive power, controlling harmonics, balancing negative sequence current and suppressing voltage flicker.

Low Voltage Static Synchronous Compensator

Svc Static Var Compensator,Low Voltage Synchronous Compensator,Low Voltage Static Compensator,Low Voltage Static Synchronous Compensator,Statcom Manufacturers,Power Quality Products

FGI SCIENCE AND TECHNOLOGY CO., LTD , https://www.fgi-tech.com